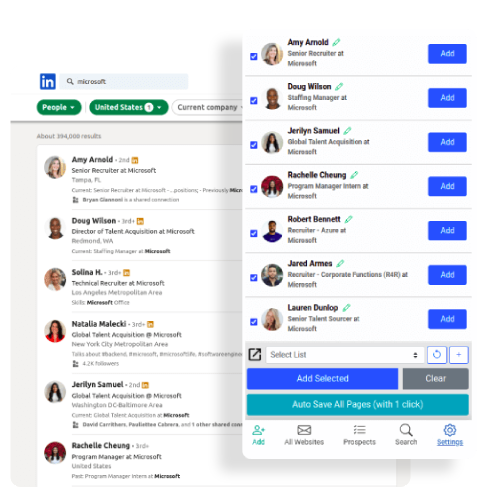

Company Details

- Employees

- 25

- Founded

- -

- Address

- 3855 Sw 153rd Dr, Beaverton,oregon 97003,united States

- Phone

- +1-5036190641

- ad****@****ink.org

- Industry

- Computer Networking Products

- NAICS

-

Software Publishers

- Website

- computeexpresslink.org

- Keywords

- Noida.

- HQ

- Beaverton, Oregon